## Voiding Control for QFN Assembly

By

Derrick Herron, Dr. Yan Liu, and Dr. Ning-Cheng Lee Indium Corporation Clinton, NY

#### **ABSTRACT**

Quad Flat No Leads (QFN) package designs receive more and more attention in electronic industry nowadays. This package offers a number of benefits including (1) small size, such as a near die-sized footprint, thin profile, and light weight; (2) easy PCB trace routing due to the use of perimeter I/O pads; (3) reduced lead inductance; (4) easy PCB trace routing; and (5) good thermal and electrical performance due to the adoption of exposed copper die-pad technology. These features make the QFN an ideal choice for many new applications where size, weight, electrical, and thermal properties are important. However, adoption of OFN often runs into voiding issues at SMT assembly. Upon reflow, outgassing of solder paste flux at the large thermal pad has difficulty escaping and inevitably results in voiding. It is well known that the presence of voids will affect the mechanical properties of joints and deteriorate the strength, ductility, creep, and fatigue life. In addition, voids could also produce spot overheating, lessening the reliability of the joints. This is particularly a concern for QFN where the primary function of thermal pads is for heat dissipation. Thermal pad voiding control at QFN assembly is a major challenge due to the large coverage area, large number of via, and low standoff. Both design and process were studied for minimizing and controlling the voiding. Eliminating the via by plugging is most effective in reducing the voiding. For an open via situation, a full thermal pad is desired for a low number of via. For a large number of via, a divided thermal pad is preferred due to better venting capability. Placement of a via at the perimeter prevents voiding caused by via. A wider venting channel has a negligible effect on voiding and reduces joint continuity. For divided thermal pada, the SMD system is more favorable than the NSMD system, with the latter suffering more voiding due to a thinner solder joint and possibly board outgassing. Performance of a divided thermal pad is dictated by venting accessability, not by the shape. Voiding reduction increases with increasing venting accessability, although introduction of a channel area compromises the continuity of solder joint. Reduced solder paste volume causes more voiding. Short profiles and long hot profiles are most promising in reducing the voiding. Voiding behavior of a QFN is similar to typical SMT voiding and increases with pad oxidation and further reflow.

Key Words: QFN, void, solder, SMT, reflow, assembly

## INTRODUCTION

Quad Flat No Leads (QFN) package designs are receiving more and more attention in electronics industry. This package offers a number of benefits including (1) small size, such as a near die-sized footprint, thin profile, and light weight; (2) easy PCB trace routing due to the use of perimeter I/O pads; (3) reduced lead inductance; and (4) good thermal and electrical performance due to the adoption of exposed copper die-pad technology. These features make the QFN an ideal choice for many new applications where size, weight, electrical, and thermal properties are important. However, adoption of QFN often runs into voiding issue during SMT assembly. Upon reflow,

outgassing of solder paste flux at the large thermal pad has difficulty escaping and inevitably results in voiding [1]. It is well known that the presence of voids will affect the mechanical properties of joints and deteriorate the strength, ductility, creep, and fatigue life [2,3,4]. In addition, voids could also produce spot overheating, lessening the reliability of joints. This is a particular concern for QFN where the primary function of thermal pads is for heat dissipation. In this study, various designs of thermal pads, stencil patterns, and reflow profiles are evaluated in order to identify the optimal condition for minimizing voiding. The effect of each variable on voiding is analyzed and presented in the paper.

## **EXPERIMENTAL DESIGN**

In this work, a dummy QFN component A-MLF68-10mm-0.5mm-DC-Sn was used with 68 peripheral pads, 10 mm long on each side, 0.5mm pitch, daisy-chained, with an Sn surface finish, as shown in Fig. 1.

Figure 1. QFN component used for voiding study.

The primary focus for voiding control is the thermal pad design on FR-4 test board, including (1) a venting channel through the solder mask at the peripheral of the thermal pad; (2) the number of microvia on the thermal pad; (3) a solder mask versus a venting channel when dividing the thermal pad; and (4) the number and shape of divided thermal pads. Impact of the solder paste volume is controlled by regulating the stencil aperture size. The effect of a soldering profile and heat history is also examined. All parameters involved are shown in Table 1.

Table 1. Parameters used in voiding study

| Parameter             | Sub parameter        | Layers            |

|-----------------------|----------------------|-------------------|

| Thermal Pad<br>on PCB | Microvia number      | 0, 16, 32, 36     |

|                       | Peripheral venting   | With and          |

|                       | for full thermal pad | without           |

|                       | Dividing method      | Solder mask,      |

|                       |                      | venting channel   |

|                       | Thermal subpad       | Square, triangle  |

|                       | shape                |                   |

|                       | Thermal subpad       | 1, 4, 8, 9        |

|                       | number               |                   |

| Stencil               | Aperture             | 85%, 100%         |

| Heat History          | Reflow profile       | Short, long cool, |

|                       |                      | long, long hot    |

|                       | Other heat treatment | Prebake, 1        |

|                       |                      | reflow, 2 reflow  |

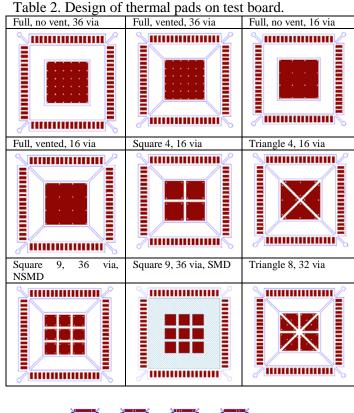

Table 2 shows the design of various thermal pads on a test board. The dimension of a full thermal pad is

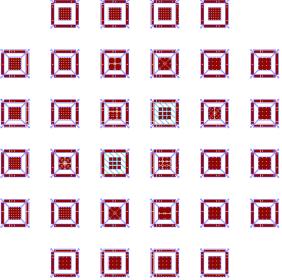

identical to that of the QFN. The surface finish for all pads, depicted in red, on the test board is immersion silver. Fig. 2 shows the layout of the test board.

Figure 2. Layout of test board EXPERIMENTAL PROCEDURE

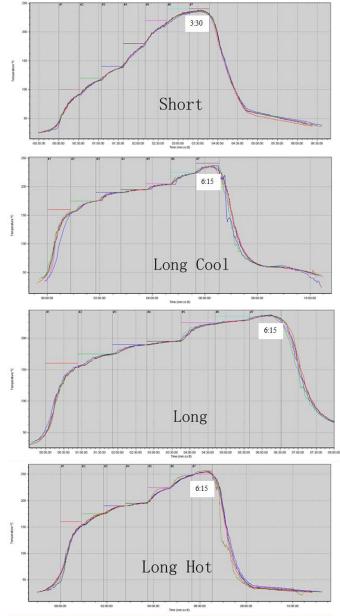

Figure 3. Reflow profiles used in the voiding study: short, long cool, long, and long hot.

A no-clean solder paste with 89% SAC387 with type 3 metal load was used for assembly of the QFN. For the

test, the solder paste was printed through a stencil with 125 micron thickness onto the test board. The aperture design is 1:1, unless otherwise specified. The QFN components were then placed and sent through a BTU oven with air atmosphere. Four reflow profiles were used, short, long cool, long, and long hot, as shown in Figure 3.

To simulate the soldering conditions of a double-sided board, the voiding performance of the following two conditions were also checked. In one instance, the board was prebaked by sending the board through an oven prior to printing the solder paste. In another, the printed board was reflowed twice.

## **VOIDING ASSESSMENT**

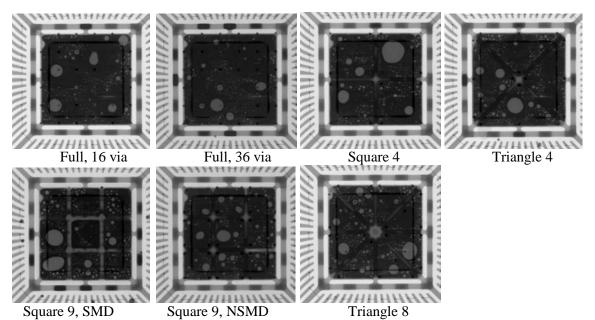

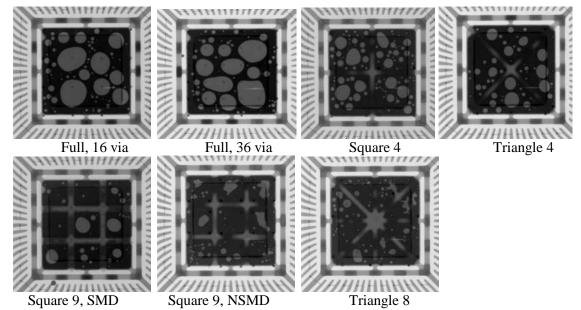

The voiding performance was determined with X-ray, as shown in Figure 4 for designs with a 0.22mm wide channel and reflowed with a long hot profile, and in Figure 5 for designs with a 0.33mm wide channel and reflowed using a long cool profile. The drastic difference in voiding behavior between the two sets demonstrates the tremendous impact of design and process conditions. Three properties are determined, as defined in Table 3. For some solder joints, cross-sectioning was also conducted in order to elucidate the characteristics of voiding.

Table 3. Definition of three voiding properties.

| Property      | Definition                              |  |

|---------------|-----------------------------------------|--|

| Discontinuity | Percentage of area under the QFN        |  |

|               | thermal pad where the vertical metal    |  |

|               | continuity from QFN to PCB surface is   |  |

|               | interrupted                             |  |

| Void Average  | Average of multiple QFNs for void       |  |

|               | area percentage within the metallic pad |  |

|               | of QFN                                  |  |

| Largest Void  | The largest void measured for a         |  |

|               | category of QFN joints                  |  |

Figure 4. X-ray images of QFN solder joints for designs with 0.22mm wide channel reflowed with a long hot profile.

Figure 5. X-ray images of QFN solder joints for designs with a 0.33mm wide channel reflowed with a long cool profile.

## **RESULTS**

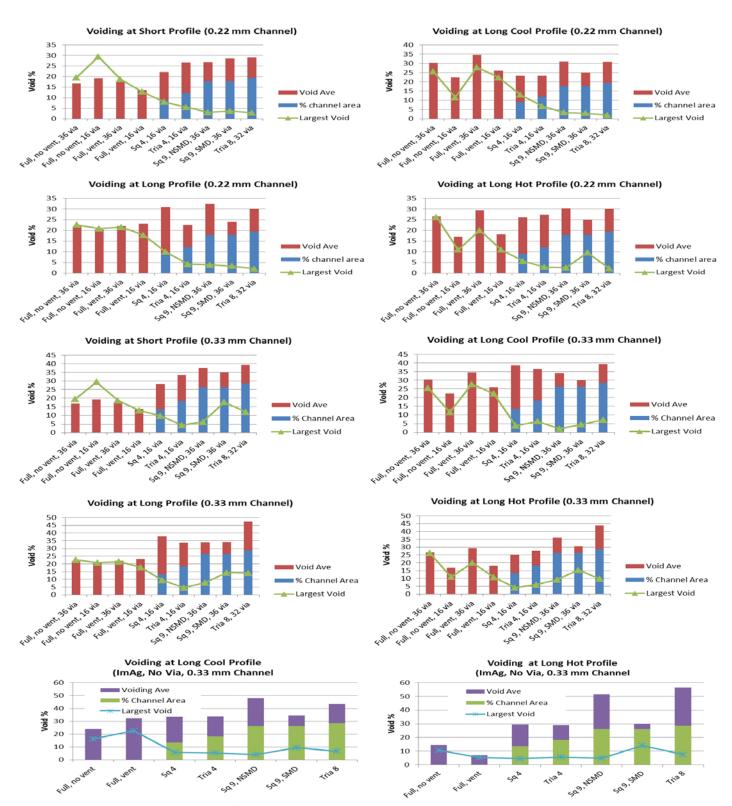

## 1. Individual Data Set

The individual data set for each of the test conditions are shown in Figure 6. A couple trends can be noticed quickly. Dividing the thermal pads into sub-units results in an abrupt drop in the largest void. In the meantime, the presence of a channel area also results in an increase in discontinuity, as reflected by the raised height of the average void plus the channel area. Apparently, the immediate effect of dividing the thermal pad is a reduction in the uncontrollable, harmful large voids, replacing it with a controlled, even distribution of discontinuity. The discontinuity of the latter may be equal or higher than the former.

Figure 6. Individual voiding data set for designs.

## 2. Effect of the Number of Via

Via is a direct contributor to voiding, mainly due to the presence of a dead corner where the entrapped flux cannot escape at the solder coalescence stage [5, 6]. This can be easily noticed in Figure 4 and 5 where the propensity of voids at via locations is particularly high for full pad solder joints. Accordingly, the voiding extent will be expected to increase with an increasing number of via. This is exactly what was observed in this study when reflowed using a long hot profile, as shown in Figure 7. When the via number is high, the discontinuity of a full pad becomes comparable with that of a divided pad, and the sporadic occurrence of large voids becomes a distinct disadvantage of the full pad design, as evidenced in Figure 6.

Since a high number of via is desired for efficient heat dissipation, the best option will be to plug the via with a solderable material, such as plated copper.

Figure 7. Effect of the number of vias on voiding when using long hot reflow profile.

The number of via bears no relation with voiding for divided pads, as evidenced in Figure 4 and 5. This is attributed to the peripheral location of via for those divided pads. Although flux may still get entrapped in those via, outgassing does not form voids easily due to the easy escape of volatiles [7].

If plugging the via is not an option, based on the benign impact of peripheral via for divided pads, it is advisable to design the via on a full pad at peripheral locations whenever possible.

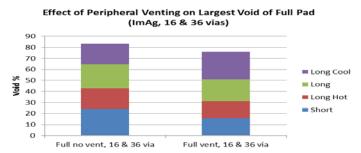

## 3. Effect of Peripheral Venting

The peripheral venting channel on a solder mask around the full pad was designed to facilitate outgassing, since the bottom of the QFN is nearly sitting on the top of board surface. Figure 8 shows that peripheral venting does reduce the size of the largest void on full pads. The effect appears to be moderate. When examing the void average, the effect of peripheral venting appears to be insignificant. Presumably, the additional venting capability due to a peripheral venting channel is negligible when compared with the clearance between the QFN and the board surface.

Figure 8. Relation between peripheral venting and the largest void for full pads.

## 4. Effect of Venting Channel Width

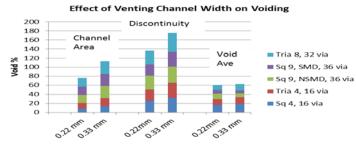

When examining Figure 4, solder bridges across the venting channel was observed for a 0.22mm wide channel. It is unclear whether these solder bridges will obstruct the outgassing significantly, thus affecting the voiding extent. Figure 9 compares the average voiding behavior of all profiles for venting channels with 0.22mm and 0.33 mm widths. An increase in channel width has no effect on the voiding average, but does cause a net increase in the channel area, and consequently an increase in discontinuity.

Figure 9. Effect of the venting channel width on average voiding behavior of all profiles

## 5. Effect of Venting Accessability

Theoretically, the closer the outgassing is to an open space or a venting channel, the less chance for a void to be developed. This venting accessability can be defined as perimeter length per unit area of metal pad. Table 4 shows the calculated venting accessability of various thermal pad designs.

Table 4. Calculated venting accessability of thermal pad designs

| Thermal pad design | Venting accessability |  |

|--------------------|-----------------------|--|

| Full pad           | 4                     |  |

| Square 4           | 8                     |  |

| Triangle 4         | 9.66                  |  |

| Square 9           | 12                    |  |

| Triangle 8         | 13.66                 |  |

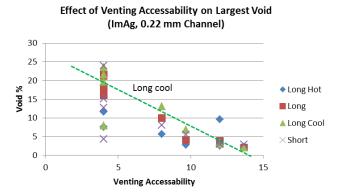

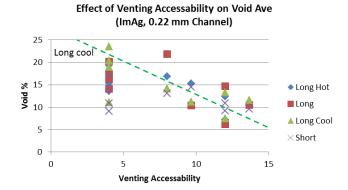

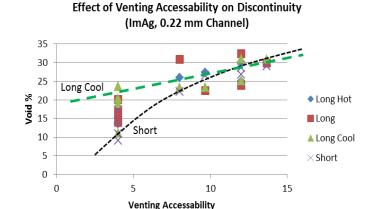

With increasing venting accessability, the void average and largest void decrease readily, especially for the long cool profile, as shown in Figures 10 and 11, respectively. However, the advantage voiding reduction is offset by the increase in discontinuity, particularly for the short profile, as shown in Figure 12. For a long cool profile, the discontinuity increases only moderately with increasing venting accessability. In other words, when the voiding is a major threat, such as designs with a high number of vias, or when a short profile is not a viable option, then a venting channel design becomes a favorable choice. Although some data scattering still exists, the venting accessability concept allows engineers to design thermal pads with a minimal need of empirical run.

Figure 1.0 Effect of venting accessability on void average

Figure 11. Effect of venting accessability on largest void

Figure 12. Effect of venting accessability on discontinuity.

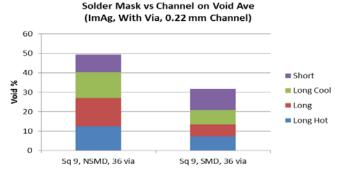

# 6. Solder Mask Defined versus Non-Solder Mask Defined

Solder does not wet onto either the solder mask or FR-4 between thermal pads. Wherever there is no solder, there is opportunity for venting. Based on the venting accessability discussed in the previous session, a thermal pad divided by either a solder mask or a venting channel on FR-4 are expected to have similar effects on voiding. However, when comparing Square 9 (SMD) with Square 9 (NSMD) designs, the void average of NSMD (venting channel design) is quite a bit higher than the SMD design, as shown in Figures 6 and 13.

Figure 13. Effect of a solder mask (SMD) or venting channel (NSMD) on void average.

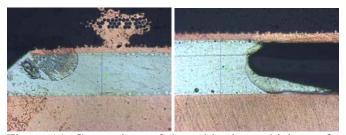

The unexpectedly high void average performance of NSMD system can be attributed partly to its thinner solder joint, as shown in Figure 14. The solder joint thickness measured is 63µ and 79µ for NSMD and SMD system, respectively. A thinner solder joint would have a greater difficulty for the void to escape [1,8]. The thicker solder joint for an SMD system is attributable to the higher solder paste volume deposited due to the presence of a solder mask at printing. The thickness of the solder mask measured is about 21µ. However, this thickness factor is considered, at best, a secondary factor.

Figure 14. Comparison of the solder layer thickness for NSMD (venting channel) and SMD systems.

Another factor, which could be the primary factor contributing to the high voiding of a NSMD system, is the outgassing of FR-4 during reflow. With the venting channel frequently blocked by the solder bridges, volatiles from FR-4 can not be vented readily and, consequently, result in more voiding under QFN. In the event of an SMD system, the solder joint is totally separated from FR-4 and thus is not affected by any FR-4 outgassing.

Use of an SMD system may have a higher value in largest void than a NSMD system, when comparing

Square 9 (SMD) and Square 9 (NSMD) in Figure 6. This may be caused by the partially blocked venting path due to the presence of solder mask, as shown in Figure 5. For a NSMD system, the venting channel is fairly open, even in the presence of a solder bridge.

Overall, the SMD system appears to be a better design than the NSMD system, in terms of reducing voiding.

Figure 15. Cross-section of a venting channel of an SMD system (left) and a NSMD system (right).

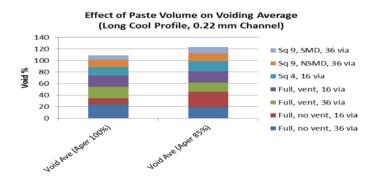

#### 7. Solder Paste Volume Effect

The effect of solder paste volume is controlled by the stencil aperture size. An aperture dimension of 1:1 is compared with an 85% opening, as shown in Figire 16. A moderately adverse effect of a smaller aperture opening is observed. Presumably, this can also be attributed to the thinner solder joints caused by a reduced solder paste volume, as discussed in the previous session.

Figure 16. Effect of solder paste volume on void average.

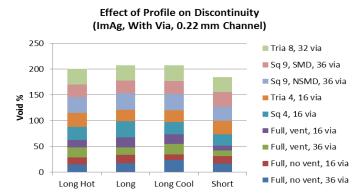

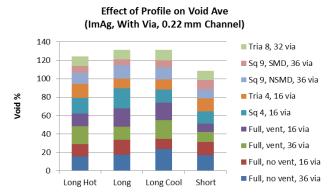

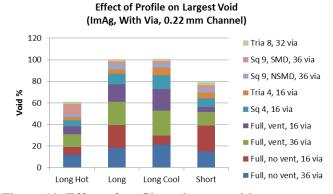

## 8. Effect of Reflow Profile

The effect of a reflow profile on voiding is shown in Figures 17, 18, and 19. Overall, both short and long hot profiles rendered lower voiding than the other profiles in between. The short profile is preferred for a low void

average, while the long hot profile is better for reducing the largest void.

Figure 17. Effect of profile on discontinuity.

Figure 18. Effect of profile on void average.

Figure 19. Effect of profile on largest void.

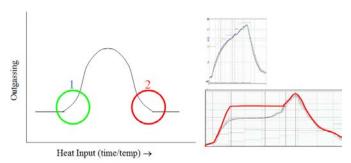

The favorable voiding behavior of short and long hot profiles can be explained by the outgassing diagram shown in Figure 20. In general, all fluxes outgas upon heating. The outgassing increases with increasing heat

input, whether it is due to an increase in temperature or time. Eventually, the volatiles get depleted, and the outgassing decreases with a further increase in heat input. For fluxes, the solvents usually vaporize during an early heating stage, followed by the volatile solids getting vaporized at a higher temperature.

Voiding in solder joints occur when volatiles are generated from the interior of a solder joint when the solder is at molten state. In order to minimize the outgassing at soldering temperatures, the outgassing rate should be minimized at temperatures above liquidus. This can be accomplished through two approaches. First, heat the flux quickly to a temperature slightly above the melting tempearture, then cool down rapidly before the volatile solids get a chance to vaporize. This corresponds to zone 1 on the diagram and can be exemplified by the upper profile on the right. Second, bring the flux to a temperature right below the melting temperature of solder, hold at that temperature until most of the volatiles are gone, then bring the flux to slightly above the melting temperature, followed by rapid cooling. This corresponds to zone 2, and can be exemplified by the lower profile on the right.

In this work, the short profile reflects the zone 1 approach, while the long hot profile reflects the zone 2 approach. Long cool and long profiles may reflect the rapid outgassing region between zones 1 and 2, thus render more voiding than both short and long hot profiles.

Figure 20. Relation between heat input and outgassing.

## 9. Effect of Prebake

Prebaking is conducted by sending the bare test boards through the reflow oven set at a short profile. The boards are then printed with solder paste, followed by QFN placement and reflow, again using the short profile. Figure 21 shows that the prebaked boards exhibit a higher void average than the fresh boards. This increase in voiding caused by the pad oxidation at prebaking indicates that, similar to voiding phenomena associated with other SMT component assemblies, a surface finish robust against oxidation will be beneficial when attempting to control voiding of QFN for a doublesided board.

#### Effect of Prebake on Void Ave (ImAg, Short Profile, 0.22 mm Channel) 160 ■ Tria 8. 32 via 140 ■ Sq 9, SMD, 36 via 120 Sq 9, NSMD, 36 via 100 ■ Tria 4, 16 via Void 80 ■ Sq 4, 16 via 60 ■ Full, vent, 16 via 40 ■ Full. vent. 36 via 20 ■ Full, no vent, 16 via ■ Full, no vent, 36 via

Figure 2.1 Effect of prebake on void average.

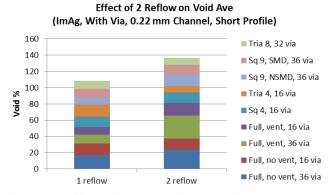

## 10. Effect of Double Reflow

A double reflow results in a higher void average, as shown in Figure 22. Apparently, this is attributable to the the additional outgassing at the second reflow and is fairly similar to voiding behavior experienced with typical SMT assembly processes.

Figure 22. Effect of double reflow on void average.

## **CONCLUSION**

Thermal pad voiding control at QFN assembly is a major challenge due to the large coverage area, large

number of via, and low standoff. Both design and process were studied for minimizing and controlling the voiding. Eliminating the via by plugging is most effective in reducing the voiding. For open via situations, a full thermal pad is desired for a low number of via. For a high number of via, a divided thermal pad is preferred due to better venting capability. Placement of via at the perimeter prevents voiding caused by via. A wider venting channel has a negligible effect on voiding and reduces joint continuity. For divided thermal pads, an SMD system is more favorable than a NSMD system, with the latter suffering more voiding due to a thinner solder joint and possibly board outgassing. Performance of a divided thermal pad is dictated by venting accessability not by the shape. Voiding reduction increases with increasing venting accessability, although the introduction of a channel area compromises the continuity of the solder joint. Reduced solder paste volume causes more voiding. Short and long hot profiles are most promising in reducing the voiding. Voiding behavior of QFN is similar to typical SMT voiding and increases with pad oxidation and further reflow.

#### REFERENCE

- 1. Ning-Cheng Lee, "Reflow soldering processes and troubleshooting: SMT, BGA, CSP, and flip chip technologies", published by Newnes, an imprint of Butterworth-Heinemann, pp.270, 2002.

- 2. D. T. Novick, "A Metallurgical Approach to Cracked Joints," *Welding J. Res. Suppl.* **52**, (4), 154S-158S (1973).

- 3. A. der Marderosian and V. Gionet, "The Effects of Entrapped Bubbles in Solder for The Attachment of Leadless Ceramic Chip Carriers" in *Proc. 21st IEEE International Reliability Physics Symposium*, Phoenix, Arizona, pp.235-241 (1983).

- 4. V. Tvergaard,"Material Failure by Void Growth to Coalescence," in Advances in Applied Mechanics, Vol. 27 (1989), Pergamon Press, pp. 83-149.

- 5. Hyoryoon Jo, Benjamin Nieman, and Ning-Cheng Lee, "Voiding of lead-free soldering at microvia", IMAPS, Denver, CO, September, 2002.

- 6. Arnab Dasgupta, Benlih Huang and Ning-Cheng Lee, "Effect of Lead-Free Alloys on Voiding at Microvia", Apex, Anaheim, CA, Feb. 23-27, 2004

- 7. H. Ladhar and S. Sethuraman, "Assembly Issues with Microvia Technologies", SMTA International, Chicago, IL, Sept. 2003.

8. Wanda B. Hance and Ning-Cheng Lee, "Voiding Mechanisms in SMT", China Lake's 17<sup>th</sup> Annual Electronics Manufacturing Seminar, 1993